要旨

スマートフォン、タブレットPCなどの最新のモバイル機器の人気が高まっていますが、その一方で、部品コスト、重量、サイズをこれまで以上に抑えつつ、システムインテグレーションや速度の向上をさらに推し進めることが必要とされています。集積回路(IC)の性能は長年にわたって大幅に改善されてきましたが、回路のパッケージング技術はその進歩に追いついてはいません。

実際のところ、パッケージングは、特にシリコン素子が小さくなるにつれて、コストと性能の両面においてのボトルネックとなっています。しかし、キルトパッケージングと呼ばれる新しい技術では、システムレベルでのICパッケージ性能の向上とコスト削減が大いに期待できます。ノートルダム大学のナノ科学技術センター、電気工学科のゲイリー H. バーンスタイン教授の研究室では、教授とクワンリン・ツェンなどの大学院生により、2次元のSiP(システムインパッケージ)という理論的枠組みと、チップ間相互接続をより効率的にするための新しいソリューションが開発されました

キルトパッケージング技術は、多くの論文やシンポジウムで紹介されています。この技術では、性能とコストパフォーマンスの向上のため、帯域幅を広げ、放熱効果を高めています。また、低電力化できるため、マイクロ波レーダーシステムや焦点面アレイといった多様な分野のワイヤレス機器で利用される見込みがあり、商業化の実現に向けた準備が進められています。

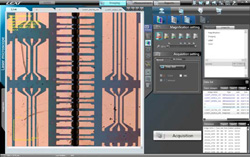

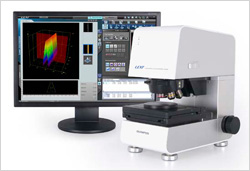

この研究室では、開発をサポートする機器として、オリンパスの3D測定レーザー顕微鏡LEXT OLS4000が使用されました。OLS4000を使うと、製造工程で微細表面形状測定ができ、正確かつ繰り返し可能な測定値を取得できます。この研究室には走査型電子顕微鏡(SEM)もありましたが、3D画像が必要とされたため、OLS4000が使用されました。触針式表面形状測定機ではなくOLS4000が選ばれたのは、3D画像の取得や粗さ測定をより速く行うことができるからです。また、スタイラスを使用すると、先端が側壁にぶつかって底部の測定ができない場合がありますが、OLS4000では、急峻なくぼみでも形状を測定できます。さらに、OLS4000は短波長レーザー光の採用により、優れた平面分解能が得られます。バーンスタイン教授は、サンプルの前処理が不要で、クリーンルームの中で素早く画像を取得できるだけでなく、表面形状測定機に比べて平面分解能に優れていることが、この装置の利点であると話しています。

キルトパッケージングの仕組み

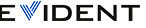

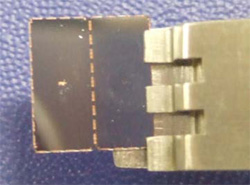

キルトパッケージングは、すでに確立されている微小電気機械システム(MEMS)から着想を得た製造技術に基づいており、基本的には単純でかつ実用的なものです。チップ同士を相互接続することによって、ICをわずか数μm間隔で2次元で並べることができます。チップの各辺からは短い端子が何本か水平に突き出ており、他のICの対応する端子と直接接続できます。この相互接続されたチップの配列をキルトといいます。キルトパッケージングの利点としては、コスト、重量、消費電力の削減や、異種デバイスの接続、高い入出力(I/O)密度、広い帯域幅(110 GHzまでの端子による挿入損失が0.1dB以下)、現在のパッケージング技術や冷却方式との互換性などが挙げられます。ノートルダム大学では、幅10μmから100μmまでのI/O構造が組み立てられました(図1-3)。

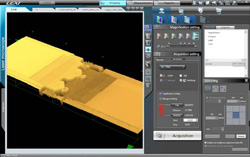

エッチングの深さの測定: キルトパッケージングでは、従来のIC製造工程に数工程が追加されます。まず、端子の溝のエッチングを行います。ノートルダム大学の研究チームでは、通常シリコン製の基板を使用しています。端子の溝のエッチングには、深掘り反応性イオンエッチング(DRIE)が採用されました。深掘りエッチングを5分間行うと、深さ20μmの溝ができます。研究過程で溝の深さの測定にスタイラスを使用したときは、先端の径が大き過ぎて溝の奥まで届きませんでしたが、OLS4000により、端子の溝の段差が正確かつ迅速に測定できました(図4)。

図1:キルトパッケージングの相互接続のイメージ図。端子が基板に深く接続されています。 |  図2:1組のチップ。コプレーナ導波路によって接続されています。 |

図3:ピンセットで持ち上げられているキルトパッケージングのチップ。端子は相互接続されています。 |  図4:端子の溝のエッチング段差測定 |

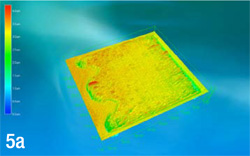

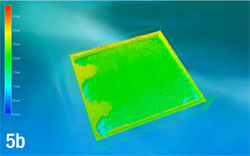

表面粗さの測定: 端子の溝のエッチングの後は、銅の電気めっきで溝を埋め、化学機械研磨(CMP)によって余分な銅を取り除きます。研磨後、研磨スラリー中の研磨粒子(一般的には超微細なシリカまたはアルミナ)がウエハー表面に付着してコンタミの原因となることがあります。RF装置の場合、特に高周波では、表面粗さが大きいとマイクロ波性能が低下します。実際に、半導体ウエハーに粒子状物質が付着すると回路不具合が起こり、最終的に歩留まり損失が発生します。OLS4000は、速くて正確な表面粗さ測定が可能で、測定には1分もかからないため、生産された製品が目的の性能を発揮するかどうかをすぐに確認できます(図5a、5b、6)。

|  |

| 図5:CMP処理直後の表面粗さ測定。(a)は、CMP処理直後の面粗さ測定の結果。(b)は、CMP後に洗浄した後で同一の測定を行った結果。 | |

| 表面粗さパラメーター | CMP後の洗浄前 | CMP後の洗浄後 | |

| 44 nm | 13 nm | |

| 十点平均粗さ Rz | 243 nm | 87 nm | |

| 56 nm | 17 nm |

図6:OLS4000の測定結果により、CMP後の洗浄前後の表面粗さパラメーターを比較できます

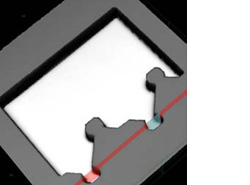

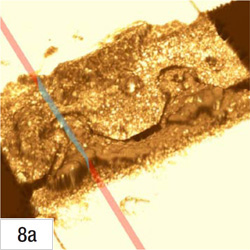

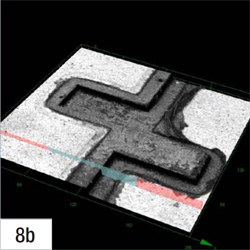

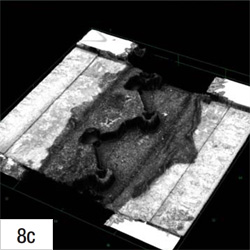

図7:組み立てられたチップの2D画像 | 垂直オフセットの測定: 洗浄の後は、分離のためにドライエッチングを行ってからチップを組み立てます(図7)。ここで、二つのチップの端子を接続する際に垂直方向のずれが大き過ぎると、組み立てに問題が生じます。接触面積が極端に変化すると、パッケージの電気的性能が悪影響を受けるため、端子接続部分が垂直方向にずれないように注意する必要があります。OLS4000を使えば、垂直方向のずれと表面形態に関する情報を取得でき、各チップの位置合わせを正確に行うことができます。 |

|  |

| 図8:端子接続部分の3D画像(a~c)。(a)のオフセットは1μm未満で、(b)と(c)は約7.3μmです。OLS4000のステッチング機能を使用すると、高解像かつ広視野の3D画像を作成できます。 | |

|  図9:端子接続部分の広視野3D表示。金属層でオンチップ相互接続をしたときと、二つのチップを外部端子で相互接続したときの高さの相違を示しています。 |

正確さと速さが極めて重要

図10:オリンパス3D測定レーザー顕微鏡LEXT OLS4000 |

OLS4000が処理過程で使用されるのは、3D測定や正確な表面粗さ測定が可能というだけでなく、これらのデータを他の測定機よりも速く取得できるからです。OLS4000では、画像の取り込み後に数秒で測定できますが、スタイラスを使用するシステムでは、プローブを面の端から端まで移動させる必要があり、はるかに時間がかかります(図10)。この研究でOLS4000を使用したことにより、これまで使用した機器と比べてより正確なカラー画像を取得できただけでなく、簡単に使えて使い勝手が良いというメリットがあることがわかりました。

現在、ノートルダム大学の研究チームは、キルトパッケージングの実用性と性能を拡張する方法や、さらに大規模展開した場合のコストパフォーマンスを上げる方法の開発に取り組んでいます。新しく設立されたIndiana Integrated Circuits, LLC社では、MEMS集積、RFシステム、高性能コンピューター処理などの用途に向けたキルトパッケージング技術を商品化しています。 |